Аппаратный сбой прототипа схемы выборки батареи

Jan 23, 2025

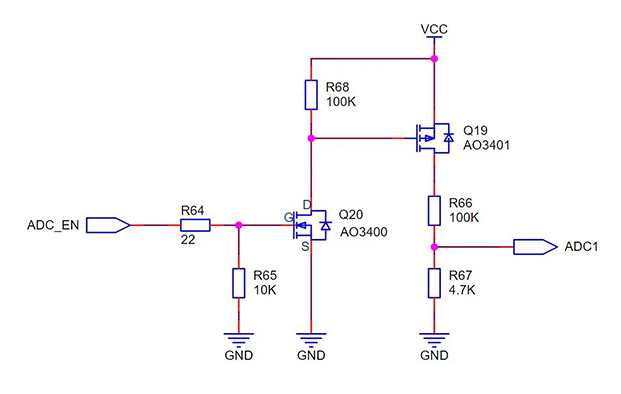

Как говорится, 'Ничего страшного, если схема и я можем работать. Если схема не работает, я буду работать.' Сегодняшняя проблема связана с аппаратным сбоем одного из участников группы. Без дальнейших пояснений давайте посмотрим: Описание проблемы: Продуктовая батарея с выборкой прототип схемы имеет вероятность дополнительного утечки тока 40uA. У одного из пяти прототипов наблюдается этот аномальный феномен. Проблема находится на PMOS, и замена PMOS полезна. Схема цепи представлена ниже:

Когда ADC_EN высокий, NMOS-транзистор Q20 включен, PMOS-транзистор Q19 включен, и ADC1 собирает напряжение VIN (ADC1≈VCC*4.7K/104.7K). Когда ADC_EN низкий, оба транзистора NMOS и PMOS выключены, и на R66 и R67 не будет утечки тока (необходимая схема для низкого потребления энергии).

Согласно схемному диаграмме, проблем нет, но фактическое отклонение заключается в том, что когда Q19 выключен, все еще наблюдается утечка тока в 40uA. Анализ причин: После тщательной проверки напряжения VIN с друзьями по группе было установлено, что напряжение батареи, соответствующее VIN, составляет 12V, то есть напряжение батареи будет выше (больше 12V) после полной зарядки. И эта схемная диаграмма скопирована из схемы сбора литиевой батареи на 4.2V...

Когда NMOS включен, напряжение VGS на обоих концах PMOS почти равно VIN (больше 12V), а используемый PMOS - AO3401, и его предельное напряжение VGS составляет ±12V. Кроме того, проблема будет решена после замены PMOS, как описано выше, поэтому предполагается, что перенапряжение VGS PMOS вызывает внутренние повреждения PMOS, что может привести к дополнительному утечке тока.

Недавние записи

26 октября 2016 года

Самый успешный инженерный подрядчик

Apr 25, 2025

Перспективы развития печатных плат (PCB)